- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

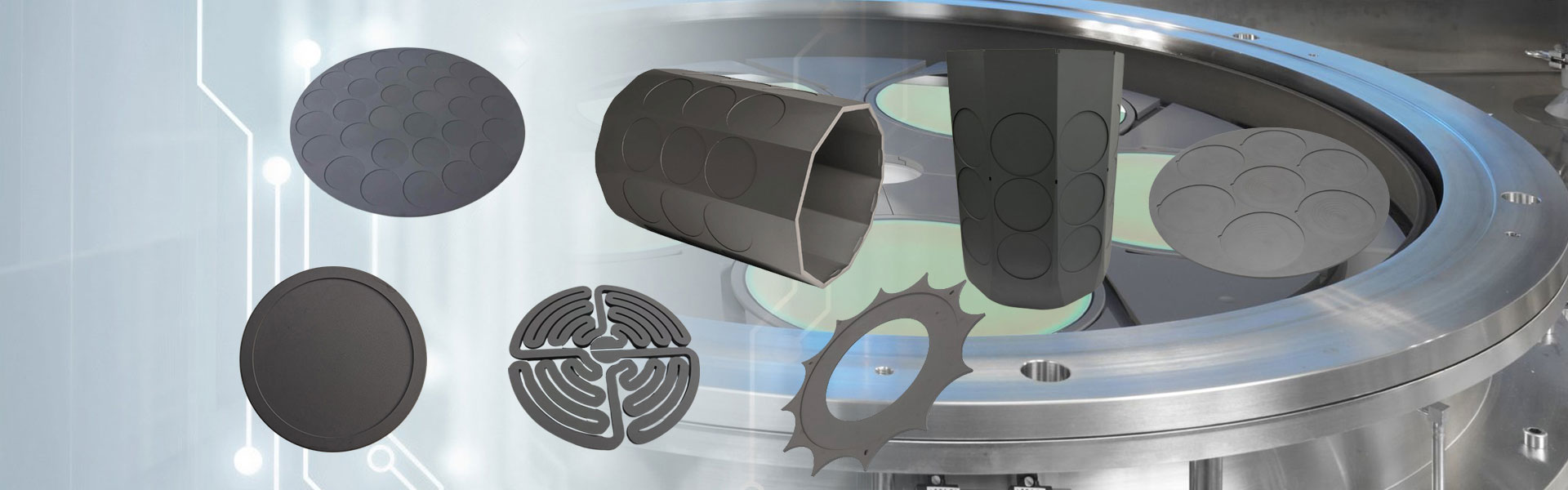

SiC-coated Graphite Plates

Semicorex SiC-coated Graphite Plates are high-purity carriers specifically engineered for the rigorous demands of SiC and GaN epitaxy, utilizing a dense CVD Silicon Carbide coating on an isostatic graphite substrate to provide a stable, chemically inert thermal barrier for high-yield wafer processing. Semicorex supplies qualified products and service for global customers.*

Send Inquiry

Semicorex SiC-coated Graphite Plates are designed to meet the challenges, serving as the high-precision interface between the reactor's heating elements and the wafer itself.

1. Advanced CVD Coating Technology:

The performance of our plates is rooted in the quality of the Silicon Carbide layer. We utilize a high-temperature Chemical Vapor Deposition (CVD) process using high-purity precursor gases (typically Methyltrichlorosilane, CH3SiCl3).

Crystalline Structure: We deposit a high-density, cubic $\beta$-SiC phase. This specific crystalline structure offers the highest possible hardness and chemical resistance.

Pore-Free Seal: Unlike sprayed or sintered coatings, our CVD process creates a molecularly bonded, non-porous surface that eliminates "gas traps," ensuring that the reactor environment remains at ultra-high vacuum levels without outgassing.

Surface Morphology: The coating is engineered with a controlled surface roughness ($R_a$), optimized to provide enough friction for stable wafer placement while remaining smooth enough to prevent particle entrapment.

2. Mechanical Design and Automated Handling Compatibility

Modern epitaxy reactors (such as those from AMAT, TEL, or Aixtron) rely on robotic handling. As seen in our precision-machined plates, every notch and hole is critical for tool uptime.

Integrated Alignment Features: Our plates feature CNC-machined notches and mounting holes (as seen in the product image) that ensure perfect centeredness during high-speed rotation.

Flatness and Parallelism: We maintain a global flatness tolerance of < 20μm. This is vital because any slight tilt in the plate leads to a temperature gradient across the wafer, resulting in "slip lines" and uneven epitaxial growth.

Thermal Mass Optimization: By precision-thinning the graphite core, we optimize the thermal mass of the SiC-coated Graphite Plates, allowing for faster ramp-up and ramp-down times, which directly increases the number of batches per day.

3. Chemical Resilience in Aggressive Environments

Epitaxial processes are inherently corrosive. Our SiC-coated Graphite Plates are specifically tested against the most aggressive cleaning and process gases:

Hydrogen (H2) Resistance: At 1,600℃, hydrogen can etch standard materials. Our β-SiC coating remains inert, protecting the graphite core from structural thinning.

HCl Vapor Cleaning: To remove "parasitic" SiC growth between batches, reactors often use HCl etching. Our coating thickness (>100μm) provides a significant "wear margin," allowing for hundreds of cleaning cycles before the plate requires refurbishing.

4. Maximizing ROI through Lifecycle Management

Switching to our high-purity plates offers a clear path to lower Cost of Ownership (CoO):

Yield Improvement: Reduced "edge exclusion" zones due to better thermal uniformity.

Extended Lifetime: Our plates typically last 2-3x longer than oxide-bonded or standard-purity alternatives.

Contamination Control: Lower metallic traces (Fe, Ni, Cr < 0.1 ppm) result in higher carrier mobility in the final semiconductor device.

Expert Note: To maximize the lifespan of your SiC-coated Graphite Plates, we recommend a "soft-start" thermal protocol for new plates to allow for controlled stress distribution within the CVD layer.