- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

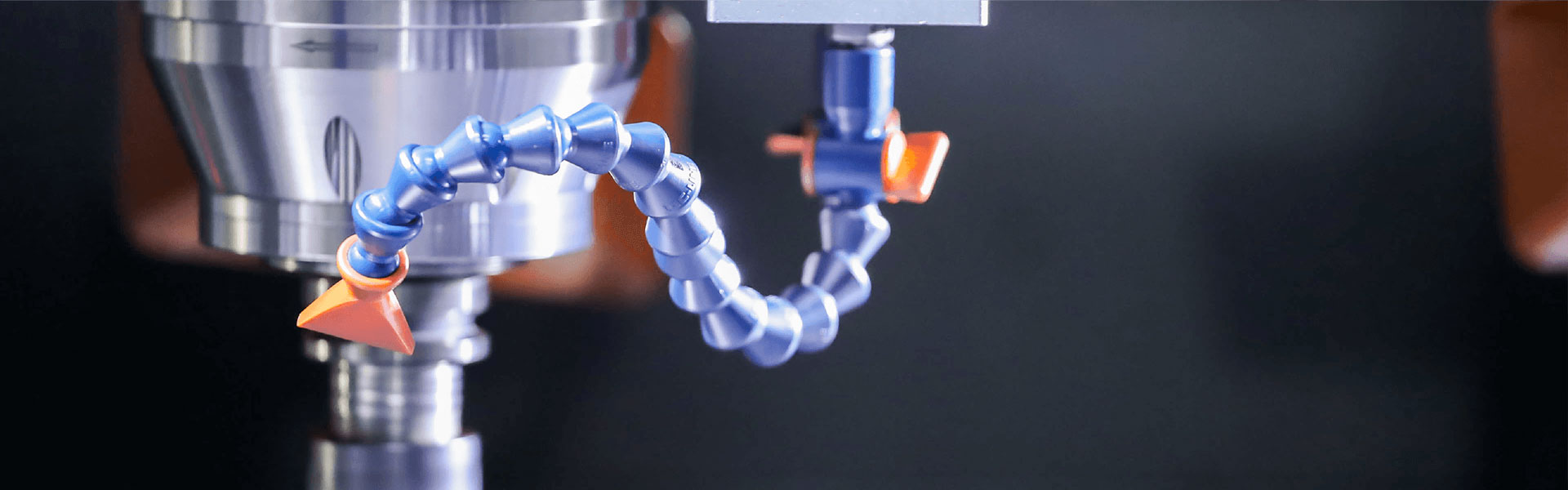

What is the process of SiC epitaxial?

In the high voltage field, particularly for high-voltage devices above 20,000V, the SiC epitaxial technology still faces several challenges. One of the main difficulties is achieving high uniformity, thickness, and doping concentration in the epitaxial layer. For the fabrication of such high-voltage devices, a 200um thick silicon carbide epitaxial wafer with excellent uniformity and concentration is required.

However, when producing thick SiC films for high-voltage devices, numerous defects, especially triangular defects, can occur. These defects can have a negative impact on the preparation of high-current devices. In particular, when large area chips are used to generate high currents, the lifetime of minority carriers (such as electrons or holes) becomes significantly reduced. This reduction in carrier lifetime can be problematic for achieving the desired forward current in bipolar devices, which are commonly used in high-voltage applications. In order to obtain the desired forward current in these devices, the minority carrier lifetime needs to be at least 5 microseconds or longer. However, the typical minority carrier lifetime parameter for SiC epitaxial wafers is around 1 to 2 microseconds.

Therefore, although the SiC epitaxial process has reached maturity and can meet the requirements of low and medium voltage applications, further advancements and technical treatments are necessary to overcome the challenges in high-voltage applications. Improvements in the uniformity of thickness and doping concentration, reduction of triangular defects, and enhancement of minority carrier lifetime are areas that require attention and development to enable the successful implementation of SiC epitaxial technology in high-voltage devices.